Vol. 45 No. 12 Dec. 2022

# 处理器分支预测攻击研究综述

刘 畅<sup>1)</sup> 杨 毅<sup>2)</sup> 李昊儒<sup>1)</sup> 邱朋飞<sup>1),2)</sup> 吕勇强<sup>3)</sup> 王海霞<sup>3)</sup> 鞠大鹏<sup>1)</sup> 汪东升<sup>1)</sup>

1)(清华大学计算机科学与技术系 北京 100084) 2)(北京邮电大学可信分布式计算与服务教育部重点实验室 北京 100867) 3)(清华大学北京信息科学与技术国家研究中心 北京 100084)

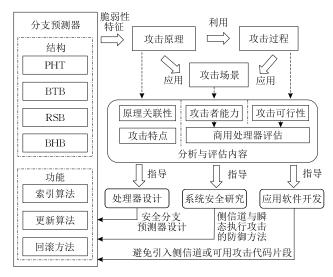

摘 要 分支预测器是现代处理器的重要微架构组件,它可有效缓解流水线的控制流冒险问题,提升处理器性能.然而,尽管分支预测器的设计越发先进,设计细节也不被处理器厂商公开,但基于分支预测器的分支预测机制存在的安全问题仍不断被研究人员曝光.利用分支预测机制,攻击者能构建侧信道或隐藏通道,从而绕过软硬件的安全边界检查.在著名的 Spectre 攻击中,分支预测器还被用来构建瞬态执行窗口,这打破了被错误预测并执行的指令对软件程序员完全透明的错误安全假设. Spectre 攻击曝光后,分支预测的安全问题越来越受到重视,相关的攻击变种与防御措施成为学术界和工业界共同关注的课题.本文从分支预测器的设计角度出发,从已公开和被研究人员逆向工程出的分支预测器设计中总结了分支预测器的工作机制,然后按分支预测器填充方式、分支预测器索引方式和分支预测和用过程等特征对现有的分支预测攻击进行归纳和整理,并总结了这些攻击的攻击模型,包括攻击场景与攻击链.随后,本文结合 Intel、AMD和 ARM等主流商用处理器的典型微体系结构,从攻击模型深入分析了各分支预测攻击的关联性、创新点和可行性,并提出一种评价分支预测类瞬态执行攻击可行性的理论方法.最后,本文讨论了分支预测攻击未来的研究趋势、相关的防御策略以及安全分支预测器设计等诸多问题.

关键词 分支预测;处理器安全;计算机微体系结构;侧信道;瞬态执行中图法分类号 TP309 **DOI**号 10.11897/SP.J.1016.2022.02475

## A Survey of Branch Prediction Attacks on Modern Processors

1) (Department of Computer Science and Technology, Tsinghua University, Beijing 100084)

<sup>2)</sup> (Ministry of Education Key Laboratory of Trustworthy Distributed Computing and Service,

Beijing University of Posts and Telecommunications, Beijing 100867)

3) (Beijing National Research Center for Information Science and Technology, Tsinghua University, Beijing 100084)

Abstract With the increasing demand for computer performance, many optimization techniques are adopted in modern processors. The branch predictors become significantly important components of computer micro-architecture for their efficiency to cope with the control hazards in pipeline. Although the design of the branch predictors has become more and more sophisticated and the details have not been disclosed by the vendors, their vulnerabilities have begun to expose. Using relevant mechanism of the branch predictors, attackers can construct side channels or covert

收稿日期:2022-01-28;在线发布日期:2022-09-27.本课题得到国家重点研发计划(2021YFB3100902)和国家自然科学基金(62072263)资助. 刘 畅,博士研究生,主要研究方向为计算机体系结构和处理器安全. E-mail: chang-li17@tsinghua. org. cn. 杨 毅,硕士研究生,主要研究方向为硬件安全和可信系统. 李昊儒,硕士研究生,主要研究方向为处理器安全. 邱朋飞,博士,副教授,主要研究方向为处理器安全. 吕勇强(通信作者),博士,副研究员,中国计算机学会(CCF)高级会员,主要研究方向为处理器安全. E-mail: luyq@tsinghua. edu. cn. 王海霞,博士,副研究员,中国计算机学会(CCF)高级会员,主要研究方向为处理器体系结构和处理器安全形式化验证. 鞠大鹏,博士,副研究员,主要研究方向计算机系统结构. 汪东升,博士,教授,博士生导师,中国计算机学会(CCF)高级会员,主要研究领域为计算机体系结构,高性能计算和系统安全.

channels to bypass the check on security boundary of software and hardware. Spectre, the notorious speculative execution attack, exploits the branch predictor to construct a transient execution window and then exploits cache side channels to access the secret data of the victim. It disproves the security assumption that the mis-predicted instructions are completely transparent to the software programmers. With the exposure of Spectre attack, the security of branch predictors aroused wild attention, many related attack variants and defense measures have been proposed. Some variants apply Spectre in a specific attack scenario, such as NetSpectre aiming at breaking other virtual machine and SGXPectre aiming at breaking into SGX. Others exploit different microarchitectural side channels during transient execution, such as SpectreRewind and SMoTherSpectre which measure the difference of time consumption on specific execution port. To better understand how these attacks exploit the branch prediction, we summarize the principles of branch predictor through the published and reverse engineered branch predictor design from the perspective of branch predictor design, and then classify the existing speculative execution attacks according to their filling and indexing methods, as well as the utilization process. Furthermore, we extract the attack models of these attacks, including 8 attack scenarios and 2 attack chains. The attack scenarios include crossprocess, cross-domain, cross-TEE, cross-VM, cross-hypervisor, cross-HT and cross-sandbox. The attack chains, consisting the side channel attack chain and the transient execution attack chain, can be merged into a model with 3 or 4 steps, including filling predictors, triggering branch instructions and exploiting the result of prediction. We use the attack model to describe the existing branch prediction attacks such as branch prediction side channels, branch prediction covert channels and transient execution attacks with or without branch prediction side channels. Furthermore, we analyse the relevance, innovativeness and feasibility of branch prediction attacks on modern processors such as Intel, AMD and ARM. Specifically, we present a theoretical method to evaluate the feasibility of transient execution attacks. Lastly, based on our analysis, we believe that automatically analysis of predictor security and secure predictor design will become the main research aspects in branch prediction security.

**Keywords** branch prediction; processor security; computer microarchitecture; side channel; transient execution

## 1 引 言

20世纪80年代以来,为了提高性能,大部分处理器实现了流水线.流水线把指令执行分成取指、译码、执行等多个阶段,充分利用硬件资源,降低了执行每条指令的时钟周期数<sup>[1]</sup>(Cycle Per Instruction, CPI).然而,由未解析的分支指令引起的控制冒险(hazard)和由数据依赖引起的数据冒险成为影响处理器性能的主要因素,这是因为在传统的流水线模型中,要想确保指令在冒险情况下正确执行,需要暂停流水线<sup>[2-4]</sup>.为了解决流水线冒险问题,以进一步提高性能,现代处理器在对程序员透明的微体系结构(以下简称微架构)层面进行了全方面、多层次的

优化,引入了包括分支预测器(Branch Preidictor)、缓存(Cache)和页表缓存(Translation Lookaside Buffer,TLB)在内的微架构部件<sup>[1]</sup>,并实现了预测执行<sup>[4]</sup>和乱序执行<sup>[5]</sup>等多种微架构性能优化技术.表1总结了主流商用处理器中普遍实现的处理器性能优化技术.

表 1 处理器性能优化技术

| 技术名称           | 技术类型 | 目的      |

|----------------|------|---------|

| 寄存器重命名[6]      | 乱序执行 | 减少数据冒险  |

| 指令重排序[7]       | 乱序执行 | 保证执行正确  |

| 指令多发射[8]       | _    | 提高指令吞吐量 |

| 分支预测[9-10]     | 预测执行 | 减少控制冒险  |

| 指令预取[11]       | 预测执行 | 减少控制冒险  |

| 存储到加载转发[12-13] | 预测执行 | 减少数据冒险  |

| 内存消歧预测[12,14]  | 预测执行 | 减少数据冒险  |

| 同步多线程[15]      | _    | 提高指令吞吐量 |

其中,分支预测已成为预测执行中不可或缺的 技术. 在设计专用分支预测部件之前,处理器通过延 迟槽[4]和分支折叠技术[16]等依赖于编译技术的静 态方法解决控制流冒险问题. 为提高程序的跨平台 能力,减小编译器负担,研究人员提出使用硬件支持 的分支预测器,通过执行流信息动态预测后续指令 的地址.从1981年提出分支预测动态算法[9]至今, 分支预测器在提高预测精度、增加速率和降低功耗 等方面不断优化,不仅在工业界有成熟的实现[17-18], 而且在学术界也通过竞赛的方式逐年升级[19].

12期

但是,在分支预测器的设计之初,设计者并没有 特别关注其存在的安全问题. 分支预测器对程序员 透明的微架构特性,以及较为完善的错误检测与回 滚(rollback)机制[14],使部分处理器厂商存在"被错 误预测并执行的指令对软件程序员完全透明"的错 误安全假设. 实际上,分支预测器与 Cache 一样,很 早就被当成侧信道和隐藏通道的来源[20-22],用于破 解 RSA 密钥[21]、绕过虚拟地址随机化(Address Space Layout Randomization, ASLR)[23] 或者窃取 SGX 中的私密数据<sup>[24]</sup>. 2018 年,著名的 Spectre 攻 击[25] 曝光,该攻击对以处理器安全为基石的系统安 全造成严重的影响. 根据 Xiong 等人的统计[26], 在 2018 至 2020 年间, Intel 在通用漏洞披露(Common Vulnerabilities and Exposures, CVE) 中公开的破坏 数据私密性的漏洞中,有超过半数是被 Spectre 相 关攻击利用的瞬态执行漏洞.

Spectre 攻击曝光后,分支预测的安全问题越来 越受到工业界和学术界的重视. 在工业界, Intel<sup>①②</sup>、 AMD<sup>®®</sup> 和 ARM<sup>®®</sup> 处理器厂商都分别公布了受 影响的处理器类型,以及相应的防御方法.同时,学 术界关于分支预测的攻防研究也迅速展开. 随着 攻击方法与防御策略的不断丰富,不少总结性的工 作出现. Canella 等人[27] 根据攻击模式总结了瞬态 执行相关攻击与防御策略,Ragab等人[14]以瞬态窗 口的触发来源为切入点总结了所有瞬态执行攻击, Xiong 等人<sup>[26]</sup> 根据侧信道类型、安全边界等分析了 瞬态执行攻击的可行性和防御策略. 然而,现有的 分析都把重点放在瞬态执行攻击上. 作为瞬态执行的 重要来源之一,分支预测机制本身的安全问题还没有 被全面地总结与分析. 本文认为,除 Spectre 外,其余 利用分支预测机制的攻击(本文简称为分支预测攻 击),包括分支预测侧信道与隐藏通道,与 Spectre 攻 击的各类变种在分支预测器的利用原理上没有本质 的区别. 例如, Branch Scope 攻击<sup>[28]</sup>与 Spectre V1 的 原理相同.

因此,本文对2007年以来学术界主要安全会议 和期刊的分支预测攻击进行了系统的归纳和分析. 文章的主要创新点如下:

- (1) 首次从分支预测的工作原理出发,全面系 统地总结了现有的主要分支预测攻击,归纳了这些 攻击的基本原理,帮助计算机系统结构设计者深入 地理解分支预测机制的安全问题来源.

- (2) 首次从攻击原理、攻击场景和攻击过程三 个角度对分支预测攻击建立全新的攻击模型,并结 合 Intel、AMD 和 ARM 等主流商用处理器的典型 微架构,从攻击模型深入分析了这些处理器在分支 预测器上的脆弱性,使硬件和系统安全研究者能对 分支预测攻击有系统性的认识和比较.

- (3) 首次提出一种分支预测类型瞬态执行攻击 可行性的评价方法,使用抽象处理器架构中攻击所 需执行指令条数的理论模型分析各分支预测攻击的 可行性,该评价方法对其余处理器微架构安全攻击 同样具有参考价值.

本文第2节介绍分支预测器的基本原理和设计 方法:第3节描述用于分析分支预测攻击的模型,包 括攻击者视角下的分支预测器模型、攻击场景和攻 击链;第4节根据分支预测器模型和攻击模型,对迄 今为止主要的分支预测攻击进行了详细介绍;第5 节分别从攻击原理、攻击场景和攻击过程出发,对各 种分支预测攻击进行整体性的比较和分析;第6节 讨论与展望分支预测机制的其它安全相关问题,包 括分支预测攻击的研究趋势、分支预测攻击的防御 策略以及安全的分支预测器设计;最后总结全文.

Speculative Execution Side Channel Mitigations. https:// software. intel. com/content/dam/develop/external/us/en/ documents/336996-speculative-execution-side-channel-mitigations. pdf, 2018. 5

Intel Analysis of Speculative Execution Side Channels. https:// newsroom. intel. com/wp-content/uploads/sites/11/2018/ 01/Intel-Analysis-of-Speculative-Execution-Side-Channels. pdf, 2018.1

AMD Product Security. https://www.amd.com/en/corporate/product-security, 2020

Software Techniques for Managing Speculation on AMD Processors. http://developer.amd.com/wp-content/resources/ Managing-Speculation-on-AMD-Processors. pdf, 2020. 9

Vulnerability of Speculative Processors to Cache Timing Side-Channel Mechanism. https://developer.arm.com/support/ arm-security-updates/speculative-processor-vulnerability,

Cache Speculation Side-channels. https://developer.arm. com/support/arm-security-updates/speculative-processorvulnerability/download-the-whitepaper, 2020.6

## 2 分支预测器设计

复杂的程序总是充斥大量的条件语句和循环语句,这些语句会根据程序上下文环境动态改变执行流.分支指令是用于修改执行流的指令,能通过一定条件决定分支方向,并附带跳转目标的地址信息.现代处理器的指令集大都实现了多类分支指令.根据分支指令是否附带跳转条件,可以分成条件分支和无条件分支,无条件分支必然跳转,条件分支则有可能跳转或不跳转,后者指的是分支被跳过且相邻的下一条指令被执行.根据分支目标是直接写在指令还是写在寄存器,还可以把分支指令分成直接分支和间接分支.

对于实现流水线的处理器,分支指令的跳转目标有时要在几个时钟周期后才被计算出来,在此期间取分支任何方向的指令预先执行都有可能出错,这种情况被称为控制流冒险<sup>[4]</sup>.为了避免控制流冒险导致流水线阻塞,现代处理器使用分支预测器来预测分支指令的跳转目标.处理器在解析分支指令后判断预测结果的正确性,如果预测正确,将不造成任何性能损失;如果预测错误,则处理器通过回滚机制重新取另一方向的指令执行<sup>[14]</sup>.

从 20 世纪 80 年代至今,为提高分支预测的精度并降低预测器的时延、面积与功耗开销,分支预测器的设计愈发复杂.为了使读者对分支预测的安全问题有全面系统的认识,本节对分支预测器设计的基本原理和关键部件的设计思想进行全面梳理和介绍.从结构角度看,尽管分支预测器的设计细节极为复杂,但都有类似的总体设计结构,即主要部件和工作原理是基本相同的.因此,2.1 节对分支预测器的主要部件进行介绍.从功能角度看,分支预测器的主要动能是实现对一条分支指令的分支方向和分支目标的预测.在分支预测器的发展过程中,实现这两类功能的部件基本是并行发展的.2.2 和 2.3 节分别对这实现这两类功能的分支预测部件的设计细节进行介绍.

### 2.1 主要部件

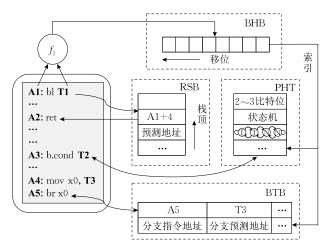

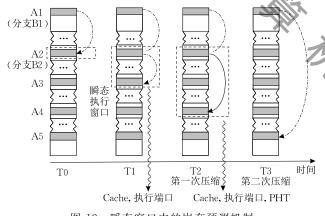

如今,主流的商用处理器实现了非常复杂的分支预测器和分支预测机制,并且实现细节未完全公开.图 1 根据部分技术手册<sup>[29-31]</sup>、部分逆向工程工作<sup>[25,28,32-34]</sup>和本研究团队在部分处理器上的实验结果,总结了现代商用处理器中主要的分支预测部件及其工作原理.图中用 ARMv8 精简指令集的分支

指令举例,展示了现代处理器中主要的四个分支预测器部件,包括分支历史缓冲区(Branch History Buffer,BHB)、模式历史表(Pattern History Table, PHT)、返回栈缓冲区(Return Stack Buffer,RSB)和分支目标缓冲区(Branch Target Buffer,BTB)。这四个部件是大部分现有分支预测安全问题的来源。

图 1 分支预测器主要部件及其工作原理示意图

BHB记录了已执行分支的历史跳转信息. 它有时作为一个系统寄存器实现,因此在部分设计中又被称为全局历史寄存器(Global History Register, GHR). 对于每一条跳转的分支指令,其指令地址和跳转目标在通过一个复杂的逻辑运算后合并到 BHB. 在分支预测中,BHB中的内容可能会与分支指令的地址进行逻辑运算后作为访问 PHT或 BTB表的索引<sup>[28,34]</sup>. 也有部分文献分别把用来索引 PHT 和 BTB的部件称为 GHR 和 BHB<sup>[35]</sup>.

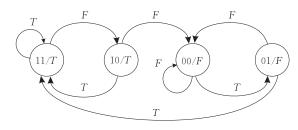

PHT 用于预测条件分支的方向. 它由分支指令地址和分支历史索引,大部分处理器的 PHT 表项是 2 到 3 位的分支预测状态机 $[^{28}]$ ,该状态机能够预测分支的跳转方向. 2 位状态机的两种实现方式如图 2 所示 $[^{4,28}]$ . 图中的四个状态中,大于 1 的两个状态表示跳转(Taken,记为 T),小于或等于 1 的两个状态表示跳转(Not Taken,记为 F). 对于索引到某个 PHT 表项的条件分支指令,该表项中状态机的状态表示了预测方向.

BTB用于预测分支的目标. 它的组织方式类似多路组相联的 Cache,记录了每条发生跳转的分支指令按照一定的哈希算法压缩后的地址和目标<sup>[34]</sup>,并对索引到组(Set)且与标签(Tag)匹配的分支进行预测.

RSB又名返回地址栈(Return Address Stack, RAS),是一种特殊的分支目标预测器,用于预测返

(a) 存在跳变的2位预测状态机(移位寄存器)

(b) 不存在跳变的2位预测状态机(饱和计数器)

图 2 2 位分支预测状态机的两种预测算法[4.28]

回指令的跳转目标. 它被设计成栈的结构. 处理器执行函数调用指令(如 x86 指令集的 call 指令或 ARM 指令集的 bl 指令)时,会把相邻的下一条指令地址写入 RSB 的顶部. 处理器执行返回指令时,栈顶地址将作为一个备选的预测目标被弹出<sup>[36-37]</sup>.

表 2 总结了各类分支指令对分支预测部件的使用方式. 预测部件表示预测分支方向和分支目标使用的部件. 索引方式表示分支地址到 PHT 或 BTB 表项的映射方式,包括直接使用存放在程序计数器 (Program Counter,PC)的分支指令地址和同时使用指令地址与分支历史(BHB)这两种方式. 更新部件表示分支执行完毕后更新的分支预测部件.

表 2 各类分支指令对分支预测部件的使用

| 分支类型    | 预测部件      | 索引方式[34] | 更新部件            |

|---------|-----------|----------|-----------------|

| 无条件直接分支 | (BTB)*    | PC       | BHB,(BTB),(RSB) |

| 条件直接分支  | (BTB),PHT | PC       | BHB,(BTB),PHT   |

| 无条件间接分支 | BTB,RSB   | PC       | BHB,(BTB),(RSB) |

| 条件间接分支  | PHT,BTB   | BHB,PC   | BHB,(BTB),PHT   |

注:\*表中添加括号表示不一定使用到该部件.比如,只有函数调用 指令更新 RSB;部分处理器的无条件直接分支能直接从指令得 到分支目标而无需使用 BTB.

#### 2.2 分支方向预测部件

分支方向预测主要由 PHT 实现. PHT 有两种设计思路,一是完全由硬件实现动态预测,二是硬件预测结合文件采样分析与编译优化<sup>[38-40]</sup>.由于程序的复杂性和处理器微架构的多样性,现代处理器主要使用前一类设计思路.表 3 总结了 1981 年到2016 年间主要相关会议和期刊上的动态分支方向预测器设计,这些设计分别在分支指令的索引方式、分支预测表设计和预测算法方面有较大的创新.表中标注的内容为创新点.

表 3 1981~2016年的主要分支方向预测器设计

| A 3 1701 - 2010                           | ・午町工女ノ       | 」 又 刀 凹 顶 豚  | I TITLE VALUE |

|-------------------------------------------|--------------|--------------|---------------|

| 分支方向预测器                                   | 索引方式         | 表项设计         | 预测算法          |

| Bimodal <sup>[41]</sup>                   | <b>✓</b>     | <b>✓</b>     | <b>✓</b>      |

| $\mathrm{GAg}^{\llbracket 42  bracket}$   | $\checkmark$ | $\checkmark$ |               |

| $\mathrm{PAg}^{\llbracket 42 \rrbracket}$ |              | $\checkmark$ |               |

| $PAp^{[42]}$                              |              | $\checkmark$ |               |

| (m,n)-correlation $[43]$                  | $\checkmark$ | $\checkmark$ |               |

| gselect <sup>[41]</sup>                   | $\checkmark$ |              |               |

| gshare <sup>[41]</sup>                    | $\checkmark$ |              |               |

| $combine^{[41]}$                          |              |              | $\checkmark$  |

| $Skewed^{[44]}$                           | $\checkmark$ | $\checkmark$ |               |

| Bi-mode <sup>[45]</sup>                   | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| $\mathrm{Agree}^{\llbracket 46  bracket}$ |              | $\checkmark$ | $\checkmark$  |

| $YAGS^{[47]}$                             |              | $\checkmark$ |               |

| Variable length path <sup>[48]</sup>      | $\checkmark$ |              |               |

| Alloyed-index <sup>[49]</sup>             | $\checkmark$ |              |               |

| perceptron-based <sup>[50]</sup>          |              |              | $\checkmark$  |

| $GEHL^{[51]}$                             | $\checkmark$ |              | $\checkmark$  |

| TAGE <sup>[19,52-53]</sup>                | $\checkmark$ |              |               |

| $ITTAGE^{[54]}$                           |              | $\checkmark$ |               |

| TAGE-SC-L <sup>[55]</sup>                 |              |              | $\checkmark$  |

#### 2.2.1 索引方式

使用 2 位状态机模型的 Bimodal 预测器是最早的动态分支预测器<sup>[9]</sup>. Bimodal 预测器实现了由 2 位状态机<sup>[41]</sup>组成的 PHT 表. 为了预测不同的分支指令,Bimodal 使用分支指令地址的低位索引表项.

在观察到分支历史是后续分支指令是否跳转的重要依据后,Yeh 等人<sup>[42]</sup>提出三种使用全局分支历史或按地址保存的分支历史(局部分支历史)索引PHT表的两级自适应预测器 GAg、PAg 和 PAp. gshare 和 gselect<sup>[41]</sup>等预测器则结合了分支历史和分支指令地址进行索引,这些预测器均使用了一个全局历史寄存器来记录历史分支跳转情况,每位表示一个历史分支是否跳转.

同时,研究人员注意到不同地址分支指令的别名(alias)问题是影响分支预测器预测精度的重要因素.别名问题指不同分支指令索引到同一预测器表项的问题.为了解决别名问题,处理器设计者设计了Skewed<sup>[44]</sup>、Bi-mode<sup>[45]</sup>和 Alloyed-index<sup>[49]</sup>等抗别名干扰的分支预测器,这些预测器使用了更加复杂的索引逻辑,并增加了辅助部件来修正由 2 位状态机得到的预测结果.

除了别名问题,研究人员还引入变长历史索引的设计以适应不同的上下文环境,如 GEHL<sup>[51]</sup>和 TA-GE<sup>[19]</sup>,后者被认为是目前最精确的分支预测器之一. 这些设计思想被用在了部分商用处理器中<sup>[18]</sup>.

现有的大部分主流商用处理器都同时实现了把指令地址与分支历史记录结合来索引 PHT 表的设计. 在索引粒度方面, Evtyushkin 等人<sup>[28]</sup>发现, Intel

系列处理器的 PHT 表按字节粒度索引,不同字节处起始的分支指令会被索引到不同的 PHT 表项.

### 2.2.2 表项设计与预测算法

除了索引机制,为了提高预测精度,研究人员还提出了更加复杂的表项设计.比如,YAGS预测器<sup>[47]</sup>在 PHT 表项中加入少量位作为标签,进一步减少了别名导致的冲突. Agree 预测器<sup>[46]</sup>则在 BTB 表项中加入偏置位用来纠正 PHT 表项的内容.

在预测算法方面,Choi 等人<sup>[56]</sup>和 Evers 等人<sup>[57]</sup>分别提出多线程和多进程环境下分支历史的更新算法.更加智能化的算法也被引入分支预测器.Jiménez 等人<sup>[50]</sup>提出使用感知器模型代替状态机,并设计了预测算法与训练算法.Tarsa 等人<sup>[58]</sup>则引入神经网络来记录分支历史.Mittal<sup>[59]</sup>总结了各种用于分支预测的智能算法与优化策略.基于感知器的方向预测器已经用于部分商用处理器<sup>[18]</sup>.

为了应对复杂多变的执行流,McFarling<sup>[41]</sup>提出同时使用多种预测机制,然后根据之前预测的正确性动态选择预测机制的组合预测器.这种锦标赛机制被沿用至今,Evtyushkin等人<sup>[28]</sup>通过逆向工程发现,Intel Skylake、Haswell 和 Sandy 处理器使用了仅分支指令地址索引和同时使用地址和分支历史索引的混合预测器,并根据这两种索引方式的预测精度,动态选择预测更准确的索引方式.

#### 2.2.3 其余设计理念

除了表 3 提到的几点外,分支方向预测还存在 很多有价值的设计理念.

- (1)引入提高预测精度的辅助部件,专门处理难预测的分支,如多层循环中的分支.包括循环退出缓冲区<sup>[60]</sup>、最内层循环迭代计数器<sup>[61]</sup>和 Wormhole<sup>[62]</sup>在内的辅助部件专门处理复杂循环.其中,循环退出缓冲区使用专门的缓冲区存放循环的迭代次数计数器,当计数器的值与循环边界值一致时修改预测方向,其设计思想被部分 Intel 处理器采用<sup>[32]</sup>.

- (2)提高预测器容量和访问效率. 相关设计包括引入多级PHT<sup>[63]</sup>、使 PHT流水线化<sup>[64]</sup>以及用傅里叶变换压缩过长的分支历史<sup>[65]</sup>.

- (3)引入专门的错误纠正部件,以尽快使分支 预测器调整到正确的预测方向. 相关设计包括对高 错误率预测状态机进行纠正的并行保守纠正器<sup>[66]</sup> 和记录错误预测下分支路径的错误历史缓冲区<sup>[67]</sup>.

### 2.3 分支目标预测部件

分支目标预测主要由 BTB 和 RSB 实现. 分支目

标预测始于 Lee 等人<sup>[10]</sup>提出的 BTB. BTB 根据当前 分支指令的地址预测其跳转目标. 由于 BTB 需要占 用较大空间来存储指令地址,并且要能够快速响应 访问,因此 BTB 的设计与多路组相联的 Cache 比较 类似<sup>[68]</sup>. 为了节省存储空间,BTB 通常不会存储完 整的指令地址. 比如,Intel 处理器中,BTB 只存储分 支目标的低 32 位,为了组成合法的分支目标,处理 器将分支指令地址的更高位和 BTB 中的 32 位拼 接<sup>[34]</sup>,这类似相对寻址机制<sup>[1]</sup>.

之后的大多数设计都是基于 BTB 的改进. 此外, 也有部分根据指令特点特殊设计的预测部件. 表 4 总 结了 1984 年至今主要相关会议和期刊上的动态分 支目标预测器设计,这些设计主要在提高预测精度、 提高容量与访问效率和减小功耗这几方面有较大的 创新. 表中标注的内容为创新点.

表 4 1981~2021 年的主要分支目标预测器设计

| 提高预测<br>精度   | 提高容量与<br>访问效率 | 减小<br>功耗     |

|--------------|---------------|--------------|

| ✓            |               |              |

|              | $\checkmark$  |              |

| $\checkmark$ |               |              |

| $\checkmark$ | $\checkmark$  |              |

| $\checkmark$ |               |              |

| $\checkmark$ |               |              |

|              |               | $\checkmark$ |

|              | $\checkmark$  |              |

|              |               | $\checkmark$ |

| $\checkmark$ |               |              |

| $\checkmark$ | $\checkmark$  |              |

|              |               |              |

## 2.3.1 提高预测精度

在提高预测精度方面,研究人员基于按指令类型使用不同预测部件的思想,设计了  $RSB^{[70]}$  (在部分处理器中称为 RAS),以及用于预测条件间接分支的  $Rehashable\ BTB^{[73]}$ 和  $Shotgun^{[77]}$ .

返回指令用于在函数调用结束后回到前一个上下文环境中. 处理器借助函数调用栈保存返回地址<sup>[1]</sup>,部分处理器也会使用一个专用寄存器存放返回地址<sup>[2]</sup>. 除了中断、异常和程序手动修改函数调用栈等特殊情况外,返回指令和函数调用指令是成对出现的<sup>[36]</sup>,即返回指令的跳转目标是与函数调用指令相邻的下一条指令地址. 根据这一特性, Kaeli 等人<sup>[69]</sup>设计了栈结构的 RSB. 这一部件在如今的大部分商用处理器中均有实现. 商用处理器常见的 RSB表项有 8条、16条或 32条等<sup>[31,37]</sup>. Mambretti 等人<sup>[79]</sup>发现, AMD 的可用 RSB表项比实际大小少一项,这是因为 RSB上保留了一个条目用于指针逻辑简

化. 在RSB为空时, Intel Skylake 等处理器会用 BTB 来预测返回指令的目标<sup>[37]</sup>. 本研究团队也在部分 ARM 处理器上观察到同样的现象. Koruyeh 等人<sup>[36]</sup> 未在 AMD 处理器观察到这一现象.

Chang 等人<sup>[71]</sup>参考分支方向预测中的分支历史索引,使用指令地址和分支历史索引 BTB,同时在 BTB 中加入分支指令的低位标签来减少别名问题. Zhang 等人<sup>[34]</sup>发现,Intel Haswell 和 Skylake 等处理器也使用了分支历史索引 BTB 的设计,并且同样实现了两种索引方式的锦标赛机制.

Ajorpaz 等人<sup>[80]</sup>分析了 BTB 替换策略对预测精度的影响,并提出基于分支历史和分支块重用情况的全局历史重用替换策略以提高预测精度.

## 2.3.2 提高访问容量与访问效率

BTB表项比 PHT表项更大,因此在不失访问效率的同时提高 BTB 容量也成为设计者关注的问题. Bray 等人<sup>[68]</sup>提出将 BTB 和 I-Cache 合并来减小存储开销,但这样放大了冲突缺失对分支预测精度的影响. Reinman 等人<sup>[72]</sup>设计了获取目标缓冲区(Fetch Target Buffer,FTB),FTB 只保存跳转分支的部分位,提高了存储空间利用率. Burcea 等人<sup>[73]</sup>设计的 Phantom-BTB 用 L2 Cache 来虚拟一个更大的 BTB 空间,从而增大了 BTB 的容量. Gupta 等人<sup>[78]</sup>设计了 Micro BTB,每个 BTB 条目存储多个分支,并且用不同类型表项来提高利用率. 这些设计在商用处理器中有部分应用,但尚未全面部署.

### 2.3.3 减小功耗

为了减小分支预测器的功耗,Lazy BTB<sup>[74]</sup>跟踪进程并预先标定每个跳转分支的 BTB 查找,以减少未跳转分支的查找;Leakage-Aware Speculative BTB<sup>[76]</sup>则预测性地激活部分条目,将其余条目置于低功耗状态.这些设计在商用处理器上的应用较少. 2.3.4 分支目标预测中的静态策略

静态策略是指某些特殊情况下,分支预测器在设计之初就确定预测分支目标的预测策略,主流商用处理器的静态处理策略包括:

- (1) 当一个条件分支指令或间接分支指令在 BTB 中不存在表项时, Intel、AMD 等处理器会预测分支不跳转<sup>[24]</sup>.

- (2)如果分支预测器的目标地址不在指令 Cache 中,Intel 等处理器会预测分支不跳转<sup>[34]</sup>.因为分支预测到分支指令解析的时间小于指令 Cache 内容缺失而访问内存的时间,所以即使预测分支跳转也会

由于取指延迟而无法带来性能上的收益. 本研究团队在部分 ARM 处理器上对 RSB 进行实验,也观察到同样的现象.

## 3 攻击模型

威胁模型或攻击模型都是描述信息安全的重要模型. 前者强调攻击对系统造成的破坏性,需要综合考虑被攻击系统的安全特性和攻击者的认知与能力,后者则更强调攻击的原理和过程<sup>①</sup>.

在分支预测攻击中,有的攻击使用了不同的分支预测部件,但使用了相同的攻击过程;有的攻击则使用了相同的攻击原理,但攻击者想要突破不同类型的安全边界.为了归纳和分析这些复杂的分支预测攻击,本文使用攻击模型对攻击建模.

在攻击模型中,攻击原理、攻击者能力、攻击目标和攻击过程都是需要研究的对象.为了方便读者把第2节介绍的分支预测器设计和实际的分支预测攻击原理联系起来,3.1节介绍了攻击者视角下的分支预测器模型.此外,3.2和3.3节分别介绍了分支预测攻击中的攻击场景模型和攻击链模型.攻击场景很好地描述了攻击者的能力和目标,而攻击链很好地描述了攻击者的攻击过程.

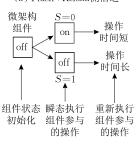

## 3.1 攻击者视角下的分支预测器模型

为了提高预测精度、提高访问速度与减小功耗, 分支预测器的设计越来越复杂,商用处理器也不再 公开设计细节.然而,复杂且不透明的分支预测器设 计无法保障分支预测器的安全性.实际上,在大多数 利用分支预测器的攻击中,攻击者往往无需了解分 支预测器的实现细节就能利用它完成攻击.

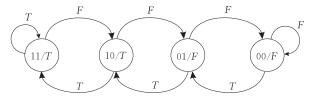

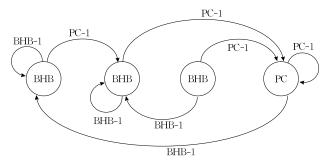

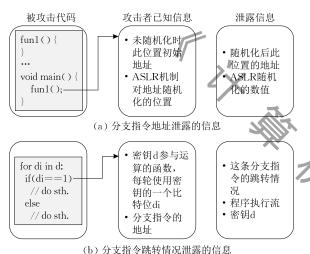

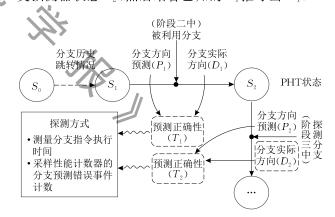

图 3 结合第 2 节的分支预测器设计和现有分支 预测攻击的攻击原理,总结了攻击者视角下的分支 预测器抽象模型. 从整体看,分支预测器的输入包括 历史分支的跳转情况、当前待预测分支指令的地址 和一些解码信息,输出是当前分支的预测目标. 分支 预测部件包括存放分支历史信息的 BHB 等部件、 预测分支跳转方向的 PHT 等部件、预测分支目标 的 BTB 和 RSB 等部件以及复杂的选择部件. 图中 的虚线表示分支历史对分支预测部件的更新;输入 分支预测部件的数据通路表示根据当前分支的地址 和分支历史计算出的索引值, f<sub>1</sub>到 f<sub>5</sub>是用于计算索

① Attack Modeling vs Threat Modeling. https://www.techre-public.com/article/attack-modeling-vs-threat-modeling/, 2006. 3

图 3 攻击者视角下的分支预测器模型

引的复杂逻辑函数. 索引方式包括仅根据分支指令地址的索引方式(用 I 表示)和结合分支地址与分支历史的索引方式(用 H 表示).

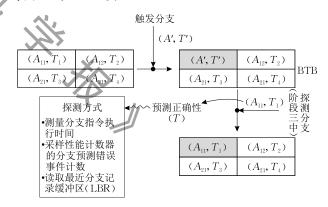

为了实现分支预测攻击,攻击者需要对预测部件的索引方式和表项规模等有比较清楚的了解.在分支预测攻击中,攻击者通过精心构造的分支历史来影响分支预测部件的内容,这一过程通常被称为误训练(mistrain)或毒化(poisoning)<sup>[25]</sup>.为了凸显攻击的底层原理,文章的后续章节把这一过程称为分支预测器填充.图3用二元组(A',T<sub>A'</sub>)来表示攻击者用于填充分支预测器的分支指令地址和该分支的实际跳转目标.填充路径有四条:①是对BHB的填充;②是对PHT的填充;③和④分别是对BTB和RSB的填充.

在实际利用分支预测器时,攻击者需要触发一个待利用分支,该分支指令的地址为 A,攻击者的目标是控制分支预测器预测的跳转目标  $T_A$ ,或者把分支预测器的预测结果  $T_A$ 作为侧信道来获取私密信息或作为隐藏通道传递信息.为了能够利用之前的填充结果,当前分支地址 A 和用于填充的分支地址 A' 应该索引到同一表项,即索引值 f(A) 与 f(A') 应该相等.

图 3 的分支预测器模型是帮助读者理解分支预测攻击过程的重要工具. 具体的攻击过程将在 4.1 至 4.4 节中具体展开介绍.

#### 3.2 攻击场景模型

在处理器安全研究中,权限等级是构建攻击场景的最重要指标.现代处理器大都实现了访问控制,把处理器使用者分级,每级有不同的数据访问权限和操作权限.

Intel 处理器定义了权限环, ring0 表示操作系统权限, ring3 表示最底层的用户进程权限[29]. Intel

还实现了虚拟化<sup>[81]</sup>,以支持虚拟机场景下虚拟机监视器(Hypervisor)和虚拟机(Virtual Machine,VM)的不同权限等级.此外,Intel 还实现了软件防护扩展(Software Guard Extensions,SGX)技术<sup>[82]</sup>以提供可信执行环境(Trusted Execution Environment,TEE),SGX 提供了安全的加密内存空间,操作系统也无法访问这块内存的内容.

ARMv8 之后的 ARM 处理器通过异常等级(Exception Level, EL)实现访问控制<sup>[30]</sup>. EL0 为用户进程权限, EL1 为普通内核或虚拟机权限, EL2 为虚拟机监视器权限, EL3 为拥有最高权限的可信执行环境 TrustZone<sup>[83]</sup>.

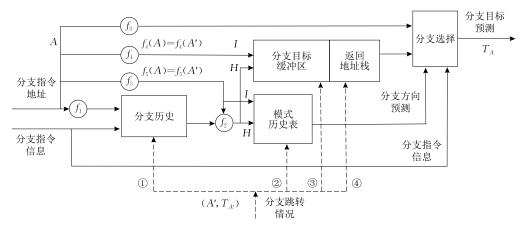

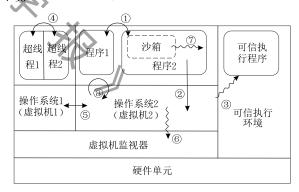

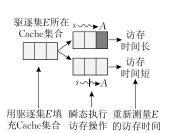

图 4 分支预测攻击场景模型

Xiong 等人<sup>[26]</sup>对瞬态执行攻击场景有很好的总结,图 4 结合 Intel 和 ARM 等商用处理器的权限等级架构,将其进一步扩展为分支预测攻击场景.

图中展示了由虚拟机监视器、操作系统(虚拟机)、普通应用程序、超线程、沙箱和可信执行环境等组成的复杂权限架构,以及8种不同的攻击场景.①是跨进程攻击场景,攻击者和攻击目标(本文简称为受害者)均是用户权限下的进程,攻击者想要获取受害者地址空间内的数据;②是跨域攻击场景,攻击者只有用户权限,而受害者是内核进程,攻击者想要破

解一些内核防御或获取内核空间数据;③是跨 TEE 攻击场景,攻击者操控恶意操作系统攻击 TEE 中的 数据; ④是同步多线程攻击场景, 攻击者和受害者 同时在一个物理核的两个不同逻辑核上执行,攻击 者目标与跨进程攻击场景相同;⑤是跨虚拟机攻击 场景,拥有内核权限的攻击者操控恶意虚拟机往外 发送任意数据包以攻击其余虚拟机,这一攻击场景 多见于网络攻击;⑥是跨 Hypervisor 攻击,攻击者 的目标是基于内核的虚拟机(Kernel-Based Virtual Machine, KVM)的攻击,攻击者想要跨过虚拟化机 制的安全边界; ⑦是跨沙箱攻击, 又称为沙箱逃逸. 沙箱是应用程序内一个特殊的执行环境,访问和操 作权限受应用程序控制,常见的跨沙箱攻击为使用 某个带恶意 JavaScript 的网站来攻击执行这段代码 的浏览器进程; ⑧是使用恶意的内核木马程序攻击 操作系统中的其它进程. 攻击者通过发布难以被分 析工具检测到的木马程序,在一定条件下泄露操作 系统或用户进程数据.

本文所构建的攻击场景涵盖了本文所整理的全部分支预测攻击. 5.2 节将结合这些攻击场景的特点,对分支预测攻击的攻击条件进行详细分析. 值得注意的是,图中没有包括的其它攻击场景,比如可信执行环境内部的跨进程攻击、跨虚拟机监视器攻击以及跨处理器攻击,也都是分支预测攻击的潜在应用场景. 受到实现难度的限制,尚未有工作在这些场景实现分支预测攻击,但不能排除它们受到分支预测攻击的可能.

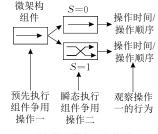

### 3.3 攻击链模型

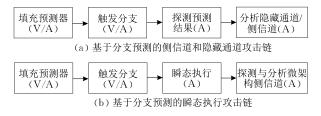

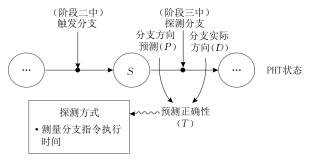

攻击链模型描述了攻击者的攻击过程,也是分析防御策略的重要工具.本文参考 Deng 等人<sup>[84-85]</sup>提出的 Cache 和 TLB 侧信道攻击模型,按照图 5 的格式描述攻击链.其中,每个阶段描述攻击者的一个操作,V表示操作由受害者(如果存在)完成,A表示操作由攻击者完成.根据对现有分支预测攻击的总结,本文把分支预测攻击的攻击链抽象成两类,一类是侧信道或隐藏通道攻击链,另一类是瞬态执行攻击链.

图 5 分支预测攻击的两类攻击链

攻击链 a 描述了将分支预测机制作为侧信道或隐藏通道的攻击. 第二阶段触发的分支指令隐藏了一些攻击者感兴趣的信息, 比如程序的执行流<sup>[23-24]</sup>或者 RSA 密钥<sup>[20,86]</sup>, 这些信息通过分支是否跳转来体现. 攻击者根据分支预测器的初始状态、对当前分支的预测结果和预测结束后分支预测器的状态来分析分支的跳转情况, 从而恢复感兴趣或者想要传递的信息. 分支预测侧信道和隐藏通道的技术细节在 4.3 节中介绍.

攻击链 b 描述了利用分支预测机制进行的瞬态执行攻击.这一类攻击中,攻击者通过第一阶段的预测器填充,使第二阶段触发的分支发生预测错误.攻击者会利用从分支指令被错误预测到处理器发现预测错误的这一时间窗口,进行私密数据访问或控制流劫持,并影响一些微架构部件的状态.处理器检测到错误的分支预测后,会通过回滚机制重新回到正确的执行路径.之后,攻击者使用已存在的一些侧信道分析技术进一步窃取私密数据. 瞬态执行攻击和相关微架构侧信道技术细节在 4.4 节中介绍.

最新的一些分支预测攻击结合了分支预测侧信道和瞬态执行攻击,在瞬态执行中利用嵌套的分支预测及分支预测器的状态变化来窃取私密数据.这类攻击相当于攻击链 b 的一个扩展,在攻击链 b 的第三步中,进一步利用了分支预测机制的特性.相关的技术细节在 4.5 节中介绍.

## 4 分支预测攻击

本文调研了现有的各种分支预测攻击,并根据第2节描述的分支预测器设计和第3节介绍的攻击模型归纳了这些攻击的特征,最终结果如表5所示.根据归纳结果,现有攻击主要使用了PHT、BTB和RSB这三个分支预测器部件,全面覆盖了3.1节中的八类攻击场景,攻击链也各有特点.4.1到4.5节对表5中分支预测攻击的技术细节进行了详细介绍.

第4节内容安排如下:4.1节介绍攻击链第一阶段中PHT、BTB和RSB和BHB四个预测器部件的填充方式;4.2节介绍攻击链第二阶段触发的分支如何索引到第一阶段填充的表项;4.3节介绍利用分支预测机制实现侧信道和隐藏通道的原理;4.4节介绍利用分支预测机制实现瞬态执行攻击的原理,以及相关微架构侧信道的一些技术细节;4.5节介绍瞬态执行窗口中的分支预测机制,以及相应的瞬态分支攻击的基本原理.

表 5 分支预测攻击的攻击模型和原理\*

|                                           | 表 3 万文顶侧攻击的攻击侯空和凉埕                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |               |           |              |               |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|-----------|--------------|---------------|

| 攻击                                        | 攻击模型                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 利用              | · • · · · · · | PC        | 利用           |               |

|                                           | 攻击链                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 攻击场景            | 部件            | 类型        | 索引           | 方式            |

| SBPA <sup>[20-22]</sup>                   | 填充 BTB(A)→触发分支(V)→时间测量与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4               | BTB           | 别名        | $\checkmark$ |               |

| Fault Attack <sup>[87]</sup>              | 填充 PHT(A)→触发分支(V)→事件测量与差分分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>4</del> ** | PHT           | 同名        | $\checkmark$ |               |

| HPC-based Attack <sup>[88]</sup>          | 离线训练(A)→填充 PHT(A)→触发分支(V)→事件测量与决策(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <del>1</del>    | PHT           | 同名        | $\checkmark$ |               |

| Jump over ASLR <sup>[23]</sup>            | 填充 BTB(A)→触发分支(V)→时间测量与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12              | BTB           | 别名        | $\checkmark$ | 侧信道           |

| Branch shadowing <sup>[24]</sup>          | 填充 BTB(V)→触发分支(A)→LBR 采样与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3               | BTB           | 别名        | _            | 内口口           |

| Template Attack <sup>[86,89]</sup>        | 离线训练(A)→填充 PHT(A)→触发分支(V)→事件测量与决策(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1               | PHT           | 同名        | $\checkmark$ |               |

| BranchScope <sup>[28]</sup>               | 填充 PHT(A)→触发分支(V)→时间或事件测量与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13              | PHT           | 同名        | $\checkmark$ |               |

| Bluethunder <sup>[90]</sup>               | 恢复 BHB(A)→填充 PHT(A)→触发分支(V)→事件测量与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3               | PHT           | 同名        | _            |               |

| RSC <sup>[91-92]</sup>                    | 填充 PHT(A)→触发分支(A)→时间测量与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 147             | PHT           | 多地址       | -***         | 隐藏            |

| $CC^{[92-93]}$                            | 填充 PHT(A)→触发分支(A)→时间测量与分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 147             | PHT           | 多地址       | _            | 通道            |

| Spectre V1 <sup>[25]</sup>                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27              | PHT           | 同名        | _            |               |

| NetSpectre <sup>[94]</sup>                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 125             | PHT           | 同名        | _            | -             |

| Speculative Interference <sup>[95]</sup>  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7               | PHT           | 同名        | _            | -             |

| SpectreRewind <sup>[96]</sup>             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7               | PHT           | 同名        | _            | -             |

| Spectre V3a <sup>[97]</sup>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2               | PHT           | 同名        |              | =             |

| Spectre V1. 1 <sup>[98]</sup>             | - 填充 PHT(V)→触发分支(V)→瞬态执行(V)→侧信道分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7               | PHT           | 同名        | _            | -             |

| SplitSpectre <sup>[79]</sup>              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7               | PHT           | 同名        | _            | -             |

| BlindSide <sup>[99]</sup>                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2               | PHT<br>BTB    | 同名        | <b>~</b>     | =             |

| SepcHammer <sup>[100]</sup>               | - <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (2)             | PHT           | 同名        |              | -             |

| BranchSpectre <sup>[101]</sup>            | 填充 PHT(V)→触发分支(V)→瞬态分支嵌套(V)→侧信道分析(A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (4)             | PHT           | 同名        | _            | -             |

| Spectre V2 <sup>[25]</sup>                | ₹Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16              | ВТВ           | 同名/<br>别名 | <b>~</b>     | -             |